Нанопроцессор - уже реальность!

Ключевые слова:

нанопроцессор

Опубликовал(а):

Шуваев Сергей Викторович

Миниатюризация электронных устройств

требует синхронной миниатюрзации используемых в них процессоров.

Значительного успеха в этой области удалось достигнуть коллективу

исследователей из Гарвардского университета. Им удалось создать

микросхему, состоящую из 496 полевых транзисторов, которую можно

запрограммировать для выполнения различных операций.

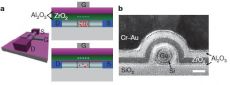

Для достижения этой цели исследователи использовали

нанонити (гетероструктура типа "ядро-оболочка" Ge-Si) в качестве

полупроводящих каналов, сам же полевой транзистор (рис.1) представлял

собой трехслойную структуру Al2O3-ZrO2-Al2O3ALD), а сток, исток и затвор были нанесены методом электронно-лучевой литографии (EBL). (толщиной 2нм-5нм-5нм), которые были получены методом нанесения атомных слоев (

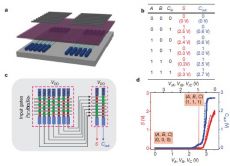

Структурным элементом полученных микросхем является

два полевых транзистора, скомпонованных таким образом, что выход одного

транзистора служит управляющим входом другого. Рассмотрим действие этой

микросхемы, запрограммированной как полный сумматор (рис.2). В этой

схеме на один из выходов подается сумма трех входных сигналов (S), а на

второй подается выходной сигнал переноса (Cout). Отдельным достижением является высокое значение предельного усиления по напряжению (10 и 4 для Cout и

S соответственно), что необходимо для практического применения. Также

крайне важно, что сигналы 0 и 1 хорошо разрешены (0 соответствует

напряжению на выходе 0-0.6 В, а 1 соответствует 2.0-2.7 В). Стоит

отметить, что предложенная схема очень просто может быть

перепрограмирована - для этого нужно всего лишь подать определенные

напряжения на сток, исток и затвор (рис.3).

Рисунок 1. а) Структура полевого транзистора, соединенного с

нанонитью. b) ПЭМ-микрофотография поперечного сечения полевого

транзистора, соединенного с нанонитью.

Рисунок 2. а) На рисунке схематически показаны стадии

нанесения микросхемы. b) Таблица истинности полного сумматора. c)

Структура микросхемы. Зеленым обозначены активные узлы. d) Зависимость

выходных напряжений (S и Cout) в зависимости от напряжения на входах (A,B и C). Касательные соответствуют предельному усилению по напряжению.

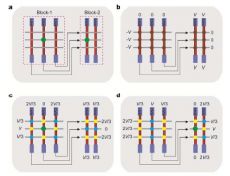

Рисунок 3. а) Микросхема до программирования. b) Все узлы

дезактивированы путем подачи напряжения -V на все затворы. c)

Программирование узла в первом блоке, путем подачи напряжения V/3 на

гейты, не пересекающиеся с узлом, и 2V/3 на сток/исток, так же не

пересекающиеся с программируемым узлом. d) Программирование узла во

втором блоке осуществляется аналогично.

http://nanometer.ru/2011/02/13/12976266877859_255139.html

|